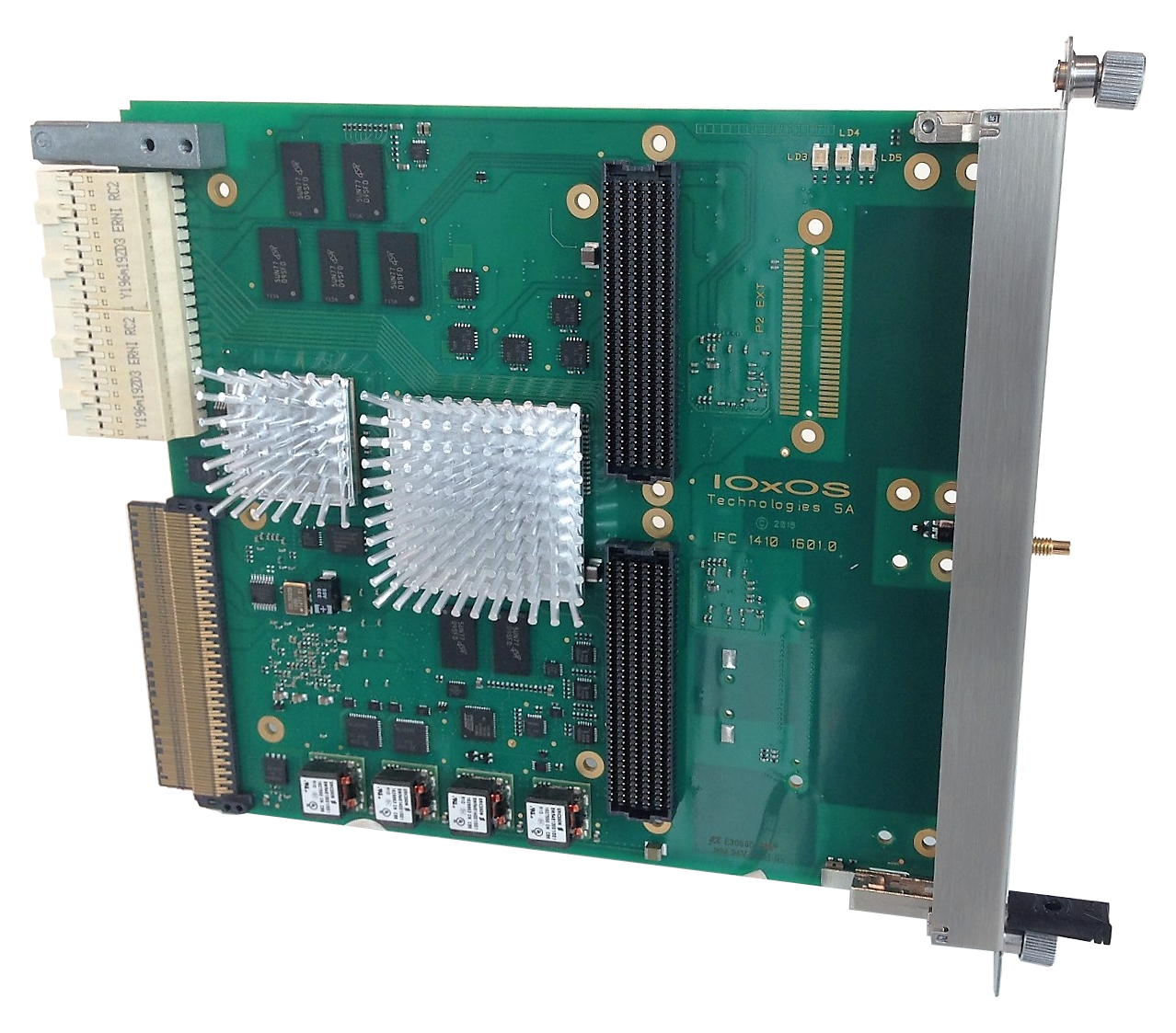

L’ADC_3210 / 3211 est une carte FMC VITA 57.1-2008 / FMC + VITA 57.4-201 doté de huit (8) canaux ADC de 14 bits à 1300 / 625 Méch/sec.

L’ADC_3210 / 3211 est basé sur la dernière génération ADC haute vitesse basse consommation avec lecture numérique via l’interface JESD204B, fonctionnant de 6,25 Gbps à 13 Gbps. Les huit (8) entrées analogiques asymétriques 50 Ohms sont fournies via des connecteurs SSMC haute fréquence. Les versions couplage AC (ADC_3210) et couplage DC (ADC_3211) sont disponibles.

Chaque canal ADC peut éventuellement être connecté à un bloc de convertisseur abaisseur numérique (DDC) à large bande, avec décimation et filtrage passe-bas/passe-haut/passe-bande ainsi qu’un mixage I/Q numérique.

L’arbre d’horloge est mis en œuvre avec un contrôleur d’horloge à faible bruit de phase à faible gigue embarqué de haute précision LMK04616, entièrement programmable par la carte porteuse. La source de référence d’horloge peut être sélectionnée à partir de l’entrée SSMC du panneau avant, de la source d’horloge FMC / FMC + ou d’un VCXO/XCO programmable à très faible bruit de phase intégré. Le FMC/FMC + ADC_3210 / 3211 intègre un mécanisme de synchronisation précis pour le double contrôleur d’horloge embarqué PLL LMK04616 et / ou des dispositifs ADC permettant de maintenir en phase plusieurs unités.

Un GPIO SSMB programmable par l’utilisateur peut être défini en tant que TRIGGER, GATE, synchronisation PLL intégrée pour la réplication CLOCK ou toute fonction spécifique à l’utilisateur intégrée dans le FPGA porteur. Un compacteur à haute vitesse avec niveau programmable (DAC) est inséré dans le chemin d’entrée GPIO.